# An ASM Thesis for BSP

Yoann Marquer and Frédéric Gava

Laboratory of Algorithms, Complexity and Logic (LACL) University of Paris-East, Créteil, France dr.marquer@gmail.com and gava@u-pec.fr

**Abstract.** The Gurevich's thesis stipulates that sequential Abstract State Machines (ASMS) capture the essence of sequential algorithms. On another side, the Bulk-Synchronous Parallel (BSP) bridging model is a well known model for HPC algorithm design. It provides a conceptual bridge between the physical implementation of the machine and the abstraction available to a programmer of that machine. The assumptions of the BSP model are thus provide portable and scalable performance predictions on HPC systems. We follow Gurevich's thesis and extend the sequential postulates in order to intuitively and realistically characterise the BSP algorithms. **Key words:** BSP, ASM, parallel algorithm, HPC, postulates, cost model.

## **1** Introduction

## 1.1 Context of the work

Nowadays, HPC (High Performance Computing) is the *norm* in many areas but it remains as difficult to have well defined paradigms and a common vocabulary as it is in the traditional sequential world. The problem arises from the difficulty to get a *taxonomy* of computer architectures and frameworks: there is a zoo of definitions of systems, languages, paradigms and programming models. Indeed, in the HPC community, several terms could be used to designate the same thing, so that misunderstandings are easy. We can cite parallel patterns [5,10] versus algorithmic skeletons [9]; shared memory (PRAM) versus thread concurrency and Direct ReMote Access (DRMA); asynchronous send/received routines (MPI, http://mi-form.org/) versus communicating processes ( $\pi$ -calculus).

In the sequential world, it is easier to classify programming languages within their paradigm (functional, object oriented, *etc.*) or by using some properties of the compilers (statically or dynamically typed, abstract machine or native code execution). This is mainly due to the fact that there is an overall consensus on what sequential computing is. For them, *formal semantics* have been often studied and there are now many tools for testing, debugging, cost analyzing, software engineering, *etc.* In this way, programmers can implement sequential algorithms using these language. And they *characterize* well the sequential algorithms.

This consensus is only fair because everyone *informally* agrees to what constitutes a sequential algorithm. And now, half a century later, there is a growing interest in defining *formally* the notion of algorithms [11]. Gurevich introduced an *axiomatic* presentation (largely machine independent) of the sequential algorithms in [11]. The main idea is that there is no language that truly represents all sequential algorithms. In fact, every algorithmic book presents the algorithm

in its own way and programming languages give too much detail. An axiomatic definition [11] of the algorithms has been mapped to the notion of Abstract state Machine (ASM, a kind of Turing machine with the appropriate level of abstraction): Every sequential algorithm can be computed by an ASM. This allows a common vocabulary about sequential algorithms. This has been studied by the ASM community for several years.

A parallel computer, or a multi-processor system, is a computer composed of more than one processor (or unit of computation). It is common to classify parallel computers (Flynn's taxonomy) by distinguishing them by the way they access the system memory (shared or distributed). Indeed, the memory access scheme influences heavily the programming method of a given system. Distributed memory systems are needed for computations using a large amount of data which does not fit in the memory of a single machine.

The set of *postulates* for sequential algorithms has been widely accepted by the scientific community. Nevertheless, to our knowledge, there is not such a work for HPC frameworks. First, due to the zoo of (informal) definitions and second, due to a lack of realistic *cost models* of common HPC architectures. In HPC, the cost measurement is not based on the complexity of an algorithm but is rather on the execution time, measured using empirical *benchmarks*. Programmers are benchmarking load balancing, communication (size of data), etc. Using such techniques, it is very difficult to explain why one code is faster than another and which one is more suitable for one architecture or another. This is regrettable because the community is failing to obtain some rigorous definitions of what HPC algorithms are. There is also a lack of studying algorithmic completeness of HPC languages. This is the basis from which to specify what can or cannot be effectively programmed. Finally, taking into account all the features of all HPC paradigms is a daunting task that is unlikely to be achieved [10]. Instead, a *bottom up strategy* (from the simplest models to the most complex) may be a solution that could serve as a basis for more general HPC models.

## 1.2 Content of the work

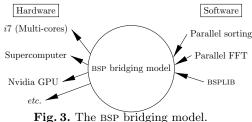

Using a bridging model [23] is a first step to this solution because it simplifies the task of the algorithm design, their programming and simplifies the reasoning of cost and ensures a better portability from one system to another. In computer science, a bridging model is thus an abstract model of a computer which provides a conceptual bridge between the physical implementation of the machine and the *abstraction* available to a programmer of that machine. We conscientiously limit our work to the Bulk-Synchronous Parallel (BSP) bridging model [2,21] because it has the advantage of being endowed with a simple model of execution. We leave more complex models to future work. Moreover, there are many different libraries and languages for programming BSP algorithms. The best known are the BSPLIB for C [12] or JAVA [20], BSML [13], PREGEL [14] for big-data, etc.

Concurrent ASMs try to capture the more general definition of asynchronous and distributed computations. We promote a rather different "bottom-up" approach consisting of restricting the model under consideration, so as to better take into account the physical architectures and in particular to highlight the algorithm execution time, which is often too difficult to assess for general models.

As a basis to this work, we must give first an axiomatic definition of BSP algorithms in the spirit of [11,15]. Basically, four postulates will be necessary. With such postulates, we can extend the ASMs of [11] to take into account the BSP model of computation. Our goal is to define a convincing set of parallel algorithms running in a predictable time and construct a model computing these algorithms only. This can be summarized by the  $ALGO_{BSP} = ASM_{BSP}$ . An interesting and novel point of this work is that the BSP cost model is preserved.

#### 1.3 Outline

The remainder of this paper is structured as follows: In Section 2 we first recall the BSP model of computation and define the postulates; Secondly, in Section 3, we give the operational semantics of  $ASM_{BSP}$  and finally, we give the main result. Section 4 concludes the paper by giving some questions with their answers (notably about the related work) and a brief outlook on future work.

## 2 Characterizing BSP algorithms

## 2.1 The BSP bridging model of computation

As the RAM model provides a unifying approach that can *bridge* the worlds of sequential *hardware* and *software*, so valiant sought [23] for a unifying model that could provide an effective (and universal) bridge between parallel hardware and software. A *bridging* model [23] allows to reduce the gap between an abstract execution (programming an algorithm) and concrete parallel systems (using a compiler and designing/optimizing a physical architecture).

The direct mode BSP model [2,21] is a bridging model that simplifies the programming of various parallel architectures using a certain level of abstraction. The assumptions of the BSP model are to provide *portable* and *scalable* performance predictions on HPC systems. Without dealing with low-level details of parallel architectures, the programmer can thus focus on algorithm design. The BSP bridging model describes a parallel architecture, an execution model, and a cost model which allows to predict the performance of a BSP algorithm on a given architecture. We now recall each of them.

A BSP computer can be specified by p computing units (**processors**), each capable of performing one elementary operation or accessing a local memory in one time unit. Processors communicate by sending a data to every other processor in g time units (gap which reflects network bandwidth inefficiency), and a barrier mechanism is able to synchronise all the processors in L time units ("latency" and the ability of the network to deliver messages under a continuous load). Such values, along with the processor's speed (*e.g.* Mflops) can be empirically determined for each architecture by executing benchmarks.

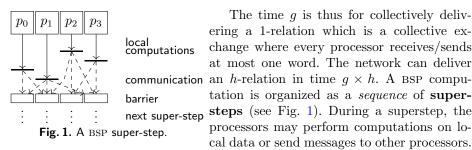

Messages are available for processing at their destinations by the next superstep, and each superstep is ended with the *barrier synchronisation* of the processors.

The execution time (cost) of a super-step s is the sum of the maximal of the local processing, the data delivery and the global synchronisation times. It is expressed by the following formula:  $\operatorname{Cost}(s) = w^s + h^s \times g + L$  where  $w^s = \max_{0 \le i < p}(w_i^s)$  is the local processing time on processor i during super-step s and  $h^s = \max_{0 \le i < p}(h_i^s)$  and  $h_i^s$  is the maximal number of words transmitted or received by the processor i. Some papers rather use the sum of words for  $h_i^s$ but modern networks are capable of sending while receiving data. The total cost (execution time) of a BSP algorithm is the sum of its super-step costs.

More comments on BSP are available in the appendix (Section B).

## 2.2 Axiomatic characterization of BSP algorithms

We follow [11] in which states are full instantaneous descriptions of an algorithm that can be conveniently formalized as first-order structures.

**Definition 1 (Structure).** A (first-order) structure X is given by:

- 1. A (potentially infinite) set  $\mathcal{U}(X)$  called the **universe** (or domain) of X

- 2. A finite set of function symbols  $\mathcal{L}(X)$  called the **signature** (language) of X

- 3. For every symbol  $s \in \mathcal{L}(X)$  an interpretation  $\overline{s}^X$  such that:

- (a) If c has arity 0 then  $\overline{c}^X$  is an element of  $\mathcal{U}(X)$

- (b) If f has an arity  $\alpha > 0$  then  $\overline{f}^X$  is an application:  $\mathcal{U}(X)^{\alpha} \to \mathcal{U}(X)$

In order to have a uniform presentation [11], we considered constant symbols in  $\mathcal{L}(X)$  as 0-ary function symbols, and relation symbols R as their indicator function  $\chi_R$ . Therefore, every symbol in  $\mathcal{L}(X)$  is a function. Moreover, partial functions can be implemented with a special symbol *undef*, and we assume in this paper that every  $\mathcal{L}(X)$  contains the boolean type  $(\neg, \wedge)$  and the equality. **Definition 2 (Term).** A term of  $\mathcal{L}(X)$  is defined by induction :

1. If c has arity 0, then c is a term

2. If f has an arity  $\alpha > 0$  and  $t_1, \ldots, t_{\alpha}$  are terms, then  $f(t_1, \ldots, t_{\alpha})$  is a term The interpretation  $\overline{t}^X$  of a term t in a structure X is defined by induction on t:

- 1. If t = c is a constant symbol, then  $\overline{t}^X \stackrel{\text{def}}{=} \overline{c}^X$

- 2. If  $t = f(t_1, ..., t_{\alpha})$  where f is a symbol of the language  $\mathcal{L}(X)$  with arity  $\alpha > 0$ and  $t_1, ..., t_{\alpha}$  are terms, then  $\overline{t}^X \stackrel{\text{def}}{=} \overline{f}^X(\overline{t_1}^X, ..., \overline{t_{\alpha}}^X)$

A formula F is a term with the particular form  $true | false | R(t_1, \ldots, t_\alpha) | \neg F | (F_1 \land F_2)$  where R is a relation symbol (ie a function with output  $\overline{true}^X$  or  $\overline{false}^X$ ) and  $t_1, \ldots, t_\alpha$  are terms. We say that a formula is true (resp. false) in X if  $\overline{F}^X = \overline{true}^X$  (resp.  $\overline{false}^X$ ). These notions are fully detailed in the appendix (Section A).

We now define the BSP algorithms as the objects verifying four postulates. The computation for every processor is done in parallel and step by step.

**Postulate 1 (Sequential Time)** A BSP algorithm A is given by:

- 1. A set of states S(A);

- 2. A set of initial states  $I(A) \subseteq S(A)$ ;

- 3. A transition function  $\tau_A : S(A) \to S(A)$ .

An **execution** of A is a sequence of states  $\overrightarrow{S} = S_0, S_1, S_2, \ldots$  such that  $S_0$  is an initial state and for every  $t \in \mathbb{N}$ ,  $S_{t+1} = \tau_A(S_t)$ .

Instead of defining a set of *final states* for the algorithms, we will say that a state  $S_t$  of an execution is **final** if  $\tau_A(S_t) = S_t$ . Indeed, in that case the execution is:  $S_0, S_1, \ldots, S_{t-1}, S_t, S_t, \ldots$  So, from an external point of view, the execution will seem to have stopped. We will say that an execution is **terminal** if it contains a final state. In that case, its **duration** is defined by:

$$\operatorname{time}(A, S_0) \stackrel{\text{def}}{=} \begin{cases} \min\left\{t \in \mathbb{N} \mid \tau_A^t(S_0) = \tau_A^{t+1}(S_0)\right\} \text{ if the execution is terminal} \\ \infty & \text{otherwise} \end{cases}$$

The BSP model defines the machine with multiple processors which have their own memory. Therefore, a state  $S_t$  of the algorithm must be a *p*-tuple  $(X_t^1, \ldots, X_t^p)^1$ . Notice that *p* is not fixed for the algorithm, so *A* can have states using different number of processors. In this paper, we will simply consider that this number is preserved during a particular execution. In other words: the number of processors is fixed by the initial state.

If  $(X^1, \ldots, X^p)$  is a state of the algorithm A, then the structures  $X^1, \ldots, X^p$  will be called *processor memories* or **local memories**. The set of the local memories of A will be denoted by M(A). Moreover, we are interested in the algorithm and not a particular implementation (for example the name of objects), therefore in the following postulate we will consider the states up to multi-isomorphism.

## Definition 3 (Multi-Isomorphism).

$\overrightarrow{\zeta}$  is a multi-isomorphism between two states  $(X^1, \ldots, X^p)$  and  $(Y^1, \ldots, Y^q)$  if p = q and  $\overrightarrow{\zeta}$  is a p-tuple of applications  $\zeta_1, \ldots, \zeta_p$  such that for every  $1 \le i \le p$ ,  $\zeta_i$  is an isomorphism between  $X^i$  and  $Y^i$ .

Postulate 2 (Abstract States) For every BSP algorithm A:

- 1. The states of A are p-tuples of structures with the same finite signature  $\mathcal{L}(A)$

- 2. S(A) and I(A) are closed by multi-isomorphism;

- 3. The transition function  $\tau_A$  preserves the universes and the numbers of processors, and commutes with multi-isomorphisms.

<sup>&</sup>lt;sup>1</sup> To simplify, we annotate units from 1 to p and not, as usual in HPC, from 0 to p-1.

For a BSP algorithm A, let X be a local memory of A,  $f \in \mathcal{L}(A)$  be a dynamic  $\alpha$ -ary function symbol, and  $a_1, \ldots, a_\alpha, b$  be elements of the universe  $\mathcal{U}(X)$ . We say that  $(f, a_1, \ldots, a_\alpha)$  is a location of X, and that  $(f, a_1, \ldots, a_\alpha, b)$  is an **update** on X at the location  $(f, a_1, \ldots, a_\alpha)$ . For example, if x is a variable then (x, 42) is an update at the location x. But symbols with arity  $\alpha > 0$  can be updated too. For example, if f is a one-dimensional array, then (f, 0, 42) is an update at the location (f, 0). If u is an update then  $X \oplus u$  is a new structure of signature  $\mathcal{L}(A)$  and universe  $\mathcal{U}(X)$  such that the interpretation of a function symbol  $f \in \mathcal{L}(A)$  is:

$$\overline{f}^{X \oplus u}(\overrightarrow{a}) \stackrel{\text{def}}{=} \begin{cases} b & \text{if } u = (f, \overrightarrow{a}, b) \\ \overline{f}^X(\overrightarrow{a}) & \text{otherwise} \end{cases}$$

(we note  $\overrightarrow{a} = a_1, \dots, a_{\alpha}$ )

For example, in  $X \oplus (f, 0, 42)$ , every symbol has the same interpretation than in X, except maybe for f because  $\overline{f}^{X \oplus (f, 0, 42)}(0) = 42$  and  $\overline{f}^{X \oplus (f, 0, 42)}(a) = \overline{f}^X(a)$  otherwise. We precised "maybe" because it may be possible that  $\overline{f}^X(0)$  is already 42.

If  $\overline{f}^{X}(\overrightarrow{a}) = b$  then the update  $(f, \overrightarrow{a}, b)$  is said **trivial** in X, because nothing has changed. Indeed, if  $(f, \overrightarrow{a}, b)$  is trivial in X then  $X \oplus (f, \overrightarrow{a}, b) = X$ .

If  $\Delta$  is a set of updates then  $\Delta$  is **consistent** if it does not contain two distinct updates with the same location. Notice that if  $\Delta$  is inconsistent, then there exists  $(f, \vec{a}, b), (f, \vec{a}, b') \in \Delta$  with  $b \neq b'$ . We assume in that case that the entire set of updates clashes:

$$\overline{f}^{X \oplus \Delta}(\overrightarrow{a}) \stackrel{\text{def}}{=} \begin{cases} b & \text{if } (f, \overrightarrow{a}, b) \in \Delta \text{ and } \Delta \text{ is consistent} \\ \overline{f}^X(\overrightarrow{a}) \text{ otherwise} \end{cases}$$

If X and Y are two local memories of the same algorithm A then there exists a unique consistent set  $\Delta = \{(f, \vec{a}, b) \mid \vec{f}^Y(\vec{a}) = b \text{ and } \vec{f}^X(\vec{a}) \neq b\}$  of non trivial updates such that  $Y = X \oplus \Delta$ . This  $\Delta$  is called the **difference** between the two local memories, and is denoted by  $Y \oplus X$ .

Let  $\vec{X} = (X^1, \ldots, X^p)$  be a state of A. According to the transition function  $\tau_A$ , the next state is  $\tau_A(\vec{X})$ , which will be denoted by  $(\tau_A(\vec{X})^1, \ldots, \tau_A(\vec{X})^p)$ . We denote by  $\Delta^i(A, \vec{X}) \stackrel{\text{def}}{=} \tau_A(\vec{X})^i \ominus X^i$  the set of updates done by the *i*-th processor of A on the state  $\vec{X}$ , and by  $\vec{\Delta}(A, \vec{X}) \stackrel{\text{def}}{=} (\Delta^1(A, \vec{X}), \ldots, \Delta^p(A, \vec{X}))$  the "multiset" of updates done by A on the state  $\vec{X}$ . In particular, if a state  $\vec{X}$  is final, then  $\tau_A(\vec{X}) = \vec{X}$ , so  $\vec{\Delta}(A, \vec{X}) = \vec{\emptyset}$ .

Let A be a BSP algorithm and T be a set of terms of  $\mathcal{L}(A)$ . We say that two states  $(X^1, \ldots, X^p)$  and  $(Y^1, \ldots, Y^q)$  of A **coincide over** T if p = q and for every  $1 \le i \le p$  and for every  $t \in T$  we have  $\overline{t}^{X^i} = \overline{t}^{Y^i}$ .

**Postulate 3 (Bounded Exploration for Processors)** For every BSP algorithm A there exists a finite set T(A) of terms such that for every state  $\overrightarrow{X}$  and  $\overrightarrow{Y}$ , if they coincide over T(A) then  $\overrightarrow{\Delta}(A, \overrightarrow{X}) = \overrightarrow{\Delta}(A, \overrightarrow{Y})$ , i.e. for every  $1 \leq i \leq p$ , we have  $\Delta^i(A, \overrightarrow{X}) = \Delta^i(A, \overrightarrow{Y})$ .

T(A) is called the **exploration witness** [11] of A. The interpretations of the terms in T(A) are called the **critical elements**, and we prove, in Section C of the appendix, that every value in an update is a critical element:

**Lemma 1 (Critical Elements).** For every state  $(X^1, \ldots, X^p)$  of A,  $\forall i \ 1 \le i \le p$ , if  $(f, \overrightarrow{a}, b) \in \Delta^i(A, \overrightarrow{X})$  then  $\overrightarrow{a}, b$  are interpretations in  $X^i$  of terms in T(A).

That implies that for every step of the computation, for a given processor, only a bounded number of terms are read or written (amount of work). In other words, each processor individually is a sequential algorithm.

**Lemma 2 (Bounded Set of Updates).** For every state  $(X^1, \ldots, X^p)$  of the BSP algorithm A, for every  $1 \le i \le p$ ,  $\#\Delta^i(A, \vec{X})$  is bounded, where #U is the number of elements of the set U.

Notice that for the moment we make no assumption on the communication between processors. Moreover, these three postulates are a "natural" extension of the ones of [11]. And by "natural", we mean that if we assume that p = 1then our postulates are exactly the same:

Lemma 3 (A Single Processor is Sequential). An algorithm verifying the first three postulates and with only one processor is a sequential algorithm.

We organize the sequence of states into **supersteps**. The communication between the processor memories occurs only during a communication phase. In order to do so, a BSP algorithm A will use two functions  $\text{comp}_A$  and  $\text{comm}_A$  indicating if A runs computations or runs communications (followed by a barrier).

**Postulate 4 (Supersteps phases)** For every BSP algorithm A there exists two applications  $comp_A : M(A) \to M(A)$  commuting with isomorphisms, and  $comm_A : S(A) \to S(A)$ , such that for every state  $(X^1, \ldots, X^p)$ :

$$\tau_A\left(X^1,\ldots,X^p\right) = \begin{cases} \left(comp_A(X^1),\ldots,comp_A(X^p)\right) \text{ if there exists } 1 \le i \le p\\ such that \ comp_A(X^i) \ne X^i\\ comm_A\left(X^1,\ldots,X^p\right) & otherwise \end{cases}$$

A **BSP algorithm** is an object verifying these four postulates, and we denote by ALGO<sub>BSP</sub> the set of the BSP algorithms. A state  $(X^1, \ldots, X^p)$  will be said in a **computation phase** if there exists  $1 \le i \le p$  such that  $\text{comp}_A(X^i) \ne X^i$ . Otherwise, the state will be said in a **communication phase**.

This requires some remarks. First, not only one processor performs the local computations but all who can. Second, we do not specified the function  $\operatorname{comm}_A$  in order to be generic about which BSP library is used. We discuss in Section 3.3 the difference between  $\operatorname{comm}_A$  and the usual communication routines in the BSP community. The communication function  $\operatorname{comm}_A$  keeps p.

Remembering that a state  $\vec{X}$  is said to be final if  $\tau_A(\vec{X}) = \vec{X}$ . Therefore, according to the fourth postulate,  $\vec{X}$  must be in a communication phase which is like a final phase that would terminate the whole execution as found in MPI.

We prove that the BSP algorithms satisfy, during a computation phase, that every processor computes independently of the state of the other processors:

**Lemma 4** (No Communication during Computation Phases). For every states  $(X^1, \ldots, X^p)$  and  $(Y^1, \ldots, Y^q)$  in a computing phase, if  $X^i$  and  $Y^j$  have the same critical elements then  $\Delta^i(A, \vec{X}) = \Delta^j(A, \vec{Y})$ .

## **3** BSP-ASM captures the BSP algorithms

The four previous postulates define the BSP algorithms from an axiomatic viewpoint but that does not mean that they have a model, or in, other words, that they are defined from an operational point of view. In the same way that the model of computation ASM captures the set of the sequential algorithms [11], we prove in this section that the  $ASM_{BSP}$  model captures the BSP algorithms.

#### 3.1 Definition and operational semantics of ASM-BSP

#### Definition 4 (ASM Program [11]).

$$\begin{split} \varPi &\stackrel{\text{def}}{=} f\left(t_1,\ldots,t_\alpha\right) := t_0 \\ &| \text{ if } F \text{ then } \Pi_1 \text{ else } \Pi_2 \text{ endif} \\ &| \text{ par } \Pi_1 \| \ldots \| \Pi_n \text{ endpar} \end{split}$$

where: f has arity  $\alpha$ ; F is a formula;  $t_1, \ldots, t_\alpha, t_0$  are terms of  $\mathcal{L}(X)$ .

Notice that if n = 0 then par  $\Pi_1 \parallel \ldots \parallel \Pi_n$  endpar is the empty program. If in if F then  $\Pi_1$  else  $\Pi_2$  endif the program  $\Pi_2$  is empty we will write simply if F then  $\Pi_1$  endif. An ASM machine [11] is a kind of Turing machine using not a tape but an abstract structure X:

Definition 5 (ASM Operational Semantics).

J.f

$$\Delta(f(t_1,\ldots,t_{\alpha}) := t_0, X) \stackrel{\text{def}}{=} \left\{ (f,\overline{t_1}^X,\ldots,\overline{t_{\alpha}}^X,\overline{t_0}^X) \right\}$$

$$\Delta(\text{if } F \text{ then } \Pi_1 \text{ else } \Pi_2 \text{ endif}, X) \stackrel{\text{def}}{=} \Delta(\Pi_i, X)$$

$$where \begin{cases} i = 1 \text{ if } F \text{ is true on } X\\ i = 2 \text{ otherwise} \end{cases}$$

$\Delta(\text{par }\Pi_1 \| \dots \| \Pi_n \text{ endpar}, X) \stackrel{\text{def}}{=} \Delta(\Pi_1, X) \cup \dots \cup \Delta(\Pi_n, X)$

Notice that the semantics of the **par** is a set of updates done simultaneously, which differs from an usual imperative framework. A state of a  $ASM_{BSP}$  machine is a *p*-tuple of memories  $(X^1, \ldots, X^p)$ . We assume that the  $ASM_{BSP}$  programs are SPMD (single Program Multiple Data) which means that at each step of computation, the  $ASM_{BSP}$  program  $\Pi$  is executed individually on each processor. Therefore  $\Pi$  induces a multiset of updates  $\overrightarrow{\Delta}$  and a transition function  $\tau_{\Pi}$ :

$$\vec{\Delta}(\Pi, (X^1, \dots, X^p)) \stackrel{\text{def}}{=} (\Delta(\Pi, X^1), \dots, \Delta(\Pi, X^p))$$

$$(\mathcal{T}_{\Pi}(X^1, \dots, X^p) \stackrel{\text{def}}{=} (X^1 \oplus \Delta(\Pi, X^1), \dots, X^p \oplus \Delta(\Pi, X^p))$$

If  $\tau_{\Pi}(\vec{X}) = \vec{X}$ , then every processor has finished its computation steps. In that case we assume that there exists a communication function to ensure the communications between processors.

**Definition 6.** An ASM<sub>BSP</sub> machine M is a triplet  $(S(M), I(M), \tau_M)$  such that:

- 1. S(M) is a set of tuples of structures with the same finite signature  $\mathcal{L}(M)$ ; S(M) and  $I(M) \subseteq S(M)$  are closed by multi-isomorphism;

- 2.  $\tau_M : S(M) \mapsto S(M)$  verifies that there exists a program  $\Pi$  and an application  $comm_M : S(M) \mapsto S(M)$  such that:

$$\tau_{M}(\vec{X}) = \begin{cases} \tau_{\Pi}(\vec{X}) \text{ if } \tau_{\Pi}(\vec{X}) \neq \vec{X} \\ comm_{M}(\vec{X}) \text{ otherwise} \end{cases}$$

- 3.  $comm_M$  verifies that:

- (1) For every state  $\vec{X}$  such that  $\tau_{\Pi}(\vec{X}) = \vec{X}$ , comm<sub>M</sub> preserves the universes and the number of processors, and commutes with multi-isomorphisms

- (2) There exists a finite set of terms  $T(comm_M)$  such that for every state  $\vec{X}$ and  $\vec{Y}$  with  $\tau_{\Pi}(\vec{X}) = \vec{X}$  and  $\tau_{\Pi}(\vec{Y}) = \vec{Y}$ , if they coincide over  $T(comm_M)$ then  $\vec{\Delta}(M, \vec{X}) = \vec{\Delta}(M, \vec{Y})$ .

We denote by ASM<sub>BSP</sub> the set of such machines. As before, a state  $\vec{X}$  is said final if  $\tau_M(\vec{X}) = \vec{X}$ . So if  $\vec{X}$  is final then  $\tau_{\Pi}(\vec{X}) = \vec{X}$  and  $\operatorname{comm}_M(\vec{X}) = \vec{X}$ .

The last conditions about the communication function may seem arbitrary, but they are required to ensure that the communication function is not a kind of magic device. For example, without these conditions, we could imagine that comm<sub>M</sub> may compute the output of the algorithm in one step, or solve the halting problem. Moreover, we presented in this definition the conditions required to prove the main theorem, but we discuss some issues in Section 3.3, and we construct an example of such communication function in the appendix (Section D).

## 3.2 The BSP-ASM thesis

We prove that  $ASM_{BSP}$  captures the computation phases of the BSP algorithms in three steps. First, we prove that during an execution, each set of updates is the interpretation of an ASM program (Lemma 8 p.16). Then, we prove an equivalence between these potentially infinite number of programs (Lemma 9 p.17). Finally, by using the third postulate, we prove in Lemma 10 p.18 that there is only a bounded number of relevant programs, which can be merged into a single one.

**Proposition 1 (BSP-ASMs capture Computations of BSP Algorithms).** For every BSP algorithm A, there exists an ASM program  $\Pi_A$  such that for every state  $\vec{X}$  in a computation phase:  $\vec{\Delta}(\Pi_A, \vec{X}) = \vec{\Delta}(A, \vec{X})$ .

Theorem 1.  $ALGO_{BSP} = ASM_{BSP}$

**Proof.** (Sketch). The full proof available in the appendix p.33. It is made by mutual inclusion. On the one hand, let A be the BSP algorithm  $(S(A), I(A), \tau_A)$ . According to the fourth postulate, there exists  $\operatorname{com}_A$  and  $\operatorname{com}_A$  such that for every state  $\vec{X}$ :

$$\tau_A(\vec{X}) = \begin{cases} \overrightarrow{\operatorname{comp}}_A(\vec{X}) \text{ if } \overrightarrow{\operatorname{comp}}_A(\vec{X}) \neq \vec{X} \\ \operatorname{comm}_A(\vec{X}) \text{ otherwise} \end{cases}$$

where  $\overrightarrow{\operatorname{comp}}_A(X^1,\ldots,X^p) = (\operatorname{comp}_A(X^1),\ldots,\operatorname{comp}_A(X^p))$ . Then, we use the the Proposition 1 to prove that:

$$\tau_A(\overrightarrow{X}) = \begin{cases} \tau_{\Pi_A}(\overrightarrow{X}) \text{ if } \tau_{\Pi_A}(\overrightarrow{X}) \neq \overrightarrow{X} \\ \operatorname{comm}_A(\overrightarrow{X}) \text{ otherwise} \end{cases}$$

According to the Lemma 5 p.13, comm<sub>A</sub> preserves the universes, the number of processors, and commutes with multi-isomorphisms. And the other properties are immediately true according to the first three postulates. Therefore A is a ASM<sub>BSP</sub> machine.

On the other hand, let M be the ASM<sub>BSP</sub> machine  $(S(M), I(M), \tau_M)$ . By definition, there exists an ASM program  $\Pi$  and an application comm<sub>M</sub> such that:

$$\tau_M(\vec{X}) = \begin{cases} \tau_{\Pi}(\vec{X}) \text{ if } \tau_{\Pi}(\vec{X}) \neq \vec{X} \\ \text{comm}_M(\vec{X}) \text{ otherwise} \end{cases}$$

We prove that M is a BSP algorithm by proving that it verifies the four postulates. The first postulate is straightforward. The second requires the Lemma 7 p.15. For the third, we prove that  $T(\Pi) = \{true\} \cup \text{Read}(\Pi) \cup \text{Write}(\Pi)$  (Definition 4 p.17) is an exploration witness for  $\tau_{\Pi}$  so  $T(M) = T(\Pi) \cup T(\text{comm}_M)$  is for M. For the fourth, we set  $\text{comp}_M(X) = X \oplus \Delta(\Pi, X)$  for every local memory X. So  $\tau_{\Pi}(\overrightarrow{X}) = \overrightarrow{\text{comp}_M}(\overrightarrow{X})$ , and we have:  $\tau_M(\overrightarrow{X}) = \begin{cases} \overrightarrow{\text{comp}_M}(\overrightarrow{X}) \text{ if } \overrightarrow{\text{comp}_M}(\overrightarrow{X}) \neq \overrightarrow{X} \\ \text{comm}_M(\overrightarrow{X}) \text{ otherwise} \end{cases}$

Therefore M is a BSP algorithm.

## 3.3 Cost model property and the function of communication

There is two more steps in order to claim that  $ASM_{BSP}$  objects are the BSP bridging model algorithms: (1) To ensure that the duration corresponds to the standard cost model and; (2) To solve issues about the communication function.

**Cost model.** If the execution begins with a communication, we assume that no computation is done for the first superstep. We remind that a state  $\overrightarrow{X_t}$  is in a computation phase if there exists  $1 \leq i \leq p$  such that  $\operatorname{comp}_A(X_t^i) \neq X_t^i$ . The computation for every processor is done in parallel, step by step, and these steps are synchronized. So, the cost in time of the computation phase is  $w \stackrel{\text{def}}{=} \max_{1 \leq i \leq p} (w_i)$ , where  $w_i$  is the number of steps done by the processor i (on memory  $X^i$ ) during the superstep.

Then the state is in a communication phase, when the messages between the processors are sent and received. Notice that  $\operatorname{comm}_A$  may require several steps in order to communicate the messages, which contrasts with the usual approach in BSP where the communication actions of a superstep are considered as one unit. But this approach would violate the third postulate, so we had to consider a step-by-step communication approach, then consider these actions as one communication phase. ASM<sub>BSP</sub> exchanges terms and we show in the appendix how formally define the size of terms. But we can imagine a machine that must further decompose the terms in order to transmit them (in bits for example). We just assume that the data are communicable in time **g** for a 1-relation.

So, during the superstep, the communication phase requires  $h \times \mathbf{g}$  steps. It remains to add the cost of the synchronization of the processors, which is assumed in the usual BSP model to be a constant **L**. Therefore, we obtained a cost property which is sound with the standard BSP cost model.

A realization of the communication. An example of a communication function for the standard BSPLIB's primitives (described in appendix Section D p.36) read (bsp\_get), write (bsp\_put), send (bsp \_send) and rcv (bsp\_move) is presented in Section D. The main difficulty is to assign an exploration witness to the communications.

**Proposition 2 (A function of communication).** A function of communication performing h-relation requiring at most h exchanges with routines for distant readings/writings and point-to-point sending of data can be design using ASM.

One may argue that the last postulate allows the communication function to do computations. To avoid it, we assume that the terms in the exploration witness T(M) can be separated between  $T(\Pi)$  and  $T(\operatorname{comm}_M)$  such that  $T(\Pi)$  is for the states in a computation phase, and that for every update  $(f, \overrightarrow{a}, b)$  of a processor  $X^i$  in a communication phase, either there exists a term  $t \in T(\operatorname{comm}_M)$ such that  $b = \overline{t}^{X^i}$ , or there exists a variable  $v \in T(\Pi)$  and a processor  $X^j$  such that  $b = \overline{t}_{\overline{v}X^j}^{X^i}$  (**representation** presented in the appendix, section D p.36). To do a computation, a term like x+1 is required, so the restriction to a variable prevents the computations of the terms in  $T(\Pi)$ . Or course, the last communication step should be able to write in  $T(\Pi)$ , and the final result should be read in  $T(\Pi)$ .

## 4 Conclusion and Future Work

## 4.1 Summary of the Contribution

In computer science, a bridging model provides a common level of *understanding* between hardware and software engineers. It provides software developers with an attractive escape route from the world of architecture-dependent parallel software [23]. The BSP bridging model allows the design of "*immortal*" (efficient and portable) parallel algorithms using a *realistic* cost model (and without any overspecification requiring the use of a large number of parameters) that can fit most distributed architectures. It has been used with success in many domains [2].

We have given an axiomatic definition of BSP algorithms by adding only one postulate to the sequential ones for sequential algorithms [11] which has been widely accepted by the scientific community. Mainly this postulate is the call of a function of communication. We abstract how communication is performed, not be restricting to a specific BSP library. We finally answer previous criticisms by defining a convincing set of parallel algorithms running in a predictable time.

Our work is relevant because it allows universality (immortal stands for BSP computing): all future BSP algorithms, whatever their specificities, will be captured by our definitions. So, our  $ASM_{BSP}$  is not just another model, it is a class model, which contains all BSP algorithms.

This small addition allows a greater *confidence* in this formal definition compared to previous work: Postulates of concurrent ASMs do not provide the same level of intuitive clarity as the postulates for sequential algorithms. But our work is limited to BSP algorithms even if it is still sufficient for many HPC and big-data applications. We have thus revisited the problem of the "*parallel ASM thesis*" *i.e.*, to provide a machine-independent definition of BSP algorithms and a proof that these algorithms are faithfully captured by ASM<sub>BSP</sub>. We also prove that the *cost model* is preserved which is the main novelty and specificity of this work compared to the traditional work about distributed or concurrent ASMs.

## 4.2 Questions and answers about this work

Why not use a BSP-Turing machine to simulate a BSP algorithm?

For sequential computing, it is known that Turing machines could simulate every algorithm or any program of any language but without a constant factor

[1]. In this way, there is not an algorithmic equivalence between Turing machines and common sequential programming languages.

Why do you use a new language  $ASM_{BSP}$  instead of using ASMs only? Indeed, each processor can be seen as a sequential ASM. So, in order to simulate one step of a BSP algorithm using several processors, we could use pids to compute sequentially the next step for each processor by using an ASM.

But if you have p processors, then each step of the BSP algorithm will be simulated by p steps. This contradicts a temporal dilation [15]: Each step should be simulated by d steps, where d is a constant depending only on the simulated program. In that case, the simulation of a BSP algorithm by a sequential ASM would require that p is constant, which means that our simulation would hold only for a fixed number of processors, and not for every number.

Why are you limited to SPMD computations?

Different codes can be run by the processors using conditionals on the "id" of the processors. For example "if pid=0 then code1 else code2" for running "code1" (*e.g.* master part) only on processor 0.

When using BSPLIB and other BSP libraries, I can switch between sequential computations and BSP ones. Why not model this kind of command?

The sequential parts can be modeled as purely asynchronous computations replicated and performed by all the processors. Or, one processor (typically the first one) is performing these computations while other processors are "waiting" with an empty computation phase.

## What happens in case of runtime errors during communications?

Typically, when one processor has a bigger number of super-steps than other processors, or when there is an out-of-bound sending or reading, it leads to a runtime error. The BSP function of communication can return a  $\perp$  value. That causes a stop of the operational semantics of the ASM<sub>BSP</sub>.

When using BSPLIB, messages received at the past superstep are dropped. Your communication function does not show this fact.

We want to be as general as possible. Perhaps a future library would allow reading data received *n* supersteps ago. Moreover, the communication function may realize some computations and is thus not a pure transmission of data. But the exploration witness forbids doing whatever. And we provide a realistic example of such a function which mainly correspond to the BSPLIB's primitives. *What about related work?*

As far as we know, some work exists to model distributed programs using ASMS [17] but none to convincingly characterize BSP algorithms. In [6], authors model the P3L set of skeletons. That allows the analyze of P3L programs using standard ASM tools but not a formal characterization of what P3L is and is not.

The first work to extend ASMs for concurrent, distributed, agent-mobile algorithms is [3]. Too many postulates are used making the comprehension hard to follow or worse (loss of confidence). A first attempt to simplify this work has been done in [18] and again simplified in [8] by the use of multiset comprehension terms to maintain a kind of bounded exploration. Then, the authors prove that ASMS captures these postulates. Moreover, we are interested in distributed (HPC) computations more than parallel (threading) ASMS.

We want to clarify one thing. The ASM thesis comes from the fact that sequential algorithms work in small steps, that is steps of bounded complexity. But the number of processors (or computing units) is unbounded for parallel algorithms, which motivated the work of [3] to define parallel algorithms with wide steps, that is steps of unbounded complexity. Hence the technicality of the presentation, and the unconvincing attempts to capture parallel algorithms [4].

In our work, we use the sequence of supersteps of the BSP bridging model to simplify the approach. Even if the number of processors is unbounded, we assume that every processor works in small step. Instead of defining a state of an execution by a meta-finite structure, we assume that a state is a *p*-tuple of structures. Instead of using a global program with "forall" commands [8], every processor runs its local program with "par" commands. Instead of relaxing the third postulate, we assume it for every processor. This approach leads to a simpler presentation, using only ground terms and tuples of ordinary structures. Notice that the second example of [8] is PRAM. There is still a last drawback: Their ASMs used an implicit share memory which is irrelevant for HPC computations. This flaw of the PRAM model was already criticized in [23].

Extending the ASMS for distributed computing is not new [4]. For example the works of [7,19] about multi-agents and data-flow programs. We believe that these postulates are more general than ours but we think that our extension still remains simple and natural for BSP computing. The authors are also not concerned about the problem of algorithm completeness using a cost model which is the heart of our work and the main advantage of the BSP model.

#### 4.3 Future Work

This work leads to many possible work. First, how adapting our work to a hierarchical extension of BSP [24] which is closer to modern HPC architectures?

Second, we are currently working on extending the work of [15] in order to give the BSP algorithmic completeness of a BSP imperative programming language. There are some concrete applications: There are many languages having a BSP-like model of execution, for example PREGEL [14] for writing large-graph algorithms. An interesting application is proving which are BSP algorithmically complete and are not. BSPLIB programs are intuitively BSP. PREGEL is a good candidate to be *not* BSP if we cannot dynamically change the graph (most recent feature). Indeed, a short-path computation using PREGEL needs n super-steps (where n is the shorter path) because a node could only communicate with its neighborhood, whereas a  $\log(p)$  super-steps exists [22]. MAPREDUCE is also an interesting use case [16]. Similarly, on can imagine proving which languages are too expressive for BSP. MPI is intuitively one of them. Last, the first author is working on postulates for more general distributed algorithm  $\dot{a}$  la MPI.

## References

T. C. Biedl, et al. Palindrome Recognition Using a Multidimensional Tape. Theor. Comput. Sci., 302(1-3):475–480, 2003.

- 14 Yoann Marquer and Frédéric Gava

- R. H. Bisseling. Parallel Scientific Computation. A Structured Approach Using BSP and MPI. Oxford University Press, 2004.

- A. Blass and Y. Gurevich. Abstract State Machines Capture Parallel Algorithms. ACM Trans. Comput. Log., 4(4):578–651, 2003.

- E. Börger and K.-D. Schewe. Concurrent Abstract State Machines. Acta Inf., 53(5):469–492, 2016.

- 5. F. Cappello and M. Snir. On Communication Determinism in HPC Applications. In Computer Communications and Networks (ICCCN), pages 1–8. IEEE, 2010.

- 6. A. Cavarra and A. Zavanella. A Formal Model for the Parallel Semantics of p3l. In *ACM Symposium on Applied Computing (SAC)*, pages 804–812, 2000.

- A. Cavarra. A Data-Flow Approach to Test Multi-agent ASMs Formal Asp. Comput., 23(1):21–41, 2011.

- F. Ferrarotti, K.-D. Schewe, L. Tec, and Q. Wang. A New Thesis Concerning Synchronised Parallel Computing Simplified Parallel ASM Thesis. *Theoretical Computer Science*, 649:25–53, 2016.

- H. González-Vélez and M. Leyton. A Survey of Algorithmic Skeleton Frameworks. Software, Practrice & Experience, 40(12):1135–1160, 2010.

- S. Gorlatch. Send-receive Considered Harmful: Myths and Realities of Message Passing. ACM TOPLAS, 26(1):47–56, 2004.

- Y. Gurevich. Sequential Abstract-state Machines Capture Sequential Algorithms. ACM Trans. Comput. Log., 1(1):77–111, 2000.

- J. M. D. Hill, B. McColl, D. C. Stefanescu, M. W. Goudreau, K. Lang, S. B. Rao, T. Suel, T. Tsantilas, and R. Bisseling. BSPLIB: The BSP Programming Library. *Parallel Computing*, 24:1947–1980, 1998.

- W. Bousdira, F. Gava, L. Gesbert, F. Loulergue and G. Petiot: Functional Parallel Programming with Bulk Synchronous Parallel ML. ICNC, pages 191–196, 2010

- G. Malewicz, et al. PREGEL: A System for Large-scale Graph Processing. In Management of data, pages 135–146. ACM, 2010.

- 15. Y. Marquer. Algorithmic Completeness of Imperative Programming Languages. Fundamenta Informaticae, accepted, pages 1–27, 2017.

- M. F. Pace. BSP vs MAPREDUCE. In Computational Science (ICCS), volume 9 of Procedia Computer Science, pages 246–255. Elsevier, 2012.

- A. Prinz and E. Sherratt. Distributed ASM- Pitfalls and Solutions. In ABZ conference, LNCS, volume 8477, pages 210–215. Springer, 2014.

- K.-D. Schewe and Q. Wang. A Simplified Parallel ASM Thesis. In ABZ conference, LNCS, volume 7316, pages 341–344. Springer, 2012.

- K.-D. Schewe, F. Ferrarotti, L. Tec, Q. Wang, and W. An. Evolving Concurrent Systems: Behavioural Theory and Logic. In Australasian Computer Science Week Multiconference (ACSW), pages 1–10, 2017.

- S. Seo, E. J. Yoon, J.-H. Kim, S. Jin, J.-S. Kim, and S. Maeng. HAMA: An Efficient Matrix Computation with the MAPREDUCE Framework. In *Cloud Computing* (*CloudCom*), pages 721–726. IEEE, 2010.

- D. B. Skillicorn, J. M. D. Hill, and W. F. McColl. Questions and Answers about BSP. Scientific Programming, 6(3):249–274, 1997.

- 22. A. Tiskin. The Design and Analysis of Bulk-Synchronous Parallel Algorithms. PhD thesis, Oxford University Computing Laboratory, 1998.

- L. G. Valiant. A Bridging Model for Parallel Computation. Comm. of the ACM, 33(8):103-111, 1990.

- L. G. Valiant. A Bridging Model for Multi-core Computing. J. Comput. Syst. Sci., 77(1):154–166, 2011.

Proofs and other comments in http://lacl.fr/gava/tr-asm.pdf

## A Preliminaries of the postulates

In in section, we recall some reminders about fundamental concepts of the formalization. We consider states as first-order structures whose vocabulary or signature is a finite set of function symbols. Furthermore, it is common to say that all convenient data structures (integers, graphs, sets, *etc.*) [15] are representable by **first-order structures**. See the definitions in Section p.4.

Using structures has also the advantage to sufficiently abstracting algorithms; Each algorithm can access **elementary operations** that could be executed. For example, the Euclid algorithm is different whether we use a (native) division or simulate it using subtractions. In the same manner, a BSP algorithm could be different whether a broadcasting primitive exists or is simulated by lower-level communicating primitives such as point-to-point sending of data. These elementary operations are also called **primitives** and depend only on the architecture. Our work is thus independent of a given architecture as in the spirit of a bridging model.

In order to have a uniform presentation, as in [11] we considered constant symbols of the signature as 0-ary function symbols, and relation symbols R as their indicator function  $\chi_R$ . Therefore, every symbol in  $\mathcal{L}(X)$  is a function. In practice, the universe will be assumed infinite, for example if the data structure contains at least integers. We also assume that all the functions are total and represent partial function as total by using a special symbol *undef*. The symbols of the signature  $\mathcal{L}(X)$  are distinguished between:

- 1. Dyn X the set of **dynamic symbols**, whose interpretation can change during an execution, like a variable<sup>2</sup> x;

- 2. *Stat X* the set of **static symbols**, which have a fixed interpretation during an execution. They are also distinguished between:

- (a) Init(X), the set of **parameters**, whose interpretation depends only on the initial state, like an array in a sorting algorithm; The symbols depending on the initial state are the dynamic symbols and the parameters, so we call them the **inputs**.

The other symbols have a uniform interpretation in every state (up to isomorphism, see the Definition p.17), and they are also distinguished between:

- (b) Cons(X) the set of constructors (true and false for the booleans, 0 and S for the unary integers, etc.)

- (c)  $\operatorname{Oper}(X)$  the set of **operations** ( $\neg$  and  $\land$  for the booleans, + and  $\times$  for the integers, *etc.*)

We assume in this paper that every signature contains the boolean type (*true*, *false*,  $\neg$  and  $\land$ ) and the equality. A term *t* is said well-typed in *X* if  $\bar{t}^X \neq \overline{undef}^X$ .

*Example 1 (Booleans*  $\mathbb{B}$ ). The constructors are *true* and *false*, interpreted by two distinct values  $\overline{true}^X$  and  $\overline{false}^X$ . The basic operations are the unary symbol  $\neg$

$<sup>^2</sup>$  We assume there is no logical variables and every term is closed, so a "variable" is a dynamical symbol with arity 0.

and the binary symbol  $\wedge$ , defined by:

$$\begin{array}{c} \neg^{X}(\overline{true}^{X}) \stackrel{\text{def}}{=} \overline{false}^{X} \\ \neg^{X}(\overline{false}^{X}) \stackrel{\text{def}}{=} \overline{true}^{X} \\ \overline{\wedge}^{X}(\overline{true}^{X}, \overline{true}^{X}) \stackrel{\text{def}}{=} \overline{true}^{X} \\ \overline{\wedge}^{X}(\overline{true}^{X}, \overline{false}^{X}) \stackrel{\text{def}}{=} \overline{false}^{X} \\ \overline{\wedge}^{X}(\overline{false}^{X}, \overline{true}^{X}) \stackrel{\text{def}}{=} \overline{false}^{X} \\ \overline{\wedge}^{X}(\overline{false}^{X}, \overline{false}^{X}) \stackrel{\text{def}}{=} \overline{false}^{X} \end{array}$$

All of the other logical connectives can be defined with  $\neg$  and  $\wedge$ .

We assume in this paper that every signature contains the booleans and the equality, a binary symbol = interpreted as  $\equiv^X(a,a) = \overline{true}^X$  and  $\equiv^X(a,b) =$  $\overline{false}^X$  otherwise. We also assume that every element  $a \neq \overline{undef}^X$  of the universe  $\mathcal{U}(X)$  is representable, which means that there exists a unique term  $t_a$  formed only by constructors such that  $\overline{t_a}^X = a$ . This  $t_a$  is called the **representation** of a. This can be proven for every usual data structure [15] but this is not the point of this paper. In particular, we must assume that an element has only one type. For example, the binary integers use a different copy of  $\mathbb{N}$  than the decimal integers. In other words  $\overline{314_{10}}^X \neq \overline{100111010_2}^X$  but of course there is a bijection between the two copies. The **size** of an element is the length of its representation, in other words the number of constructors necessary to write it. For example  $|\overline{314_{10}}^X| = 3$  and  $|\overline{100111010_2}^X| = 9$ . These sizes will be used to compute the super-steps costs of the BSP algorithms.

*Example 2 (Unary integers*  $\mathbb{N}_1$ ). The constructors are the constant symbol 0 and the unary symbol S, interpreted respectively by 0 and  $n \mapsto n+1$ . Therefore, the terms have the form  $S^n 0$ , and are interpreted by  $\overline{S^n 0}^X = n$ .

Example 3 (Integers  $\mathbb{N}_b$  in base  $b \geq 2$ ). The constructors are the constant symbols  $c_0^b, \ldots, c_{b-1}^b$ , and the unary symbols  $f_0^b, \ldots, f_{b-1}^b$ , interpreted by :

1.

$$\overline{c_i^{b^X}} \stackrel{\text{def}}{=} i$$

2.  $\overline{f_i^{b^X}}(a) \stackrel{\text{def}}{=} \begin{cases} \overline{undef}^X & \text{if } a = \overline{c_0^{b^X}} \\ a \times b + i & \text{otherwise} \end{cases}$

Therefore, the terms formed only by constructors have the form  $f_{i_0}^b \dots f_{i_{n-1}}^b c_n^b$ , which we denote by  $\underline{i_n \dots i_{0_b}}$  and call the expansion of the number in base b. For example, the decimal expansion of  $314 = (3 \times 10 + 1) \times 10 + 4$  is  $\underline{314}_{10} = f_4^{10} f_1^{10} c_3^{10}$ , and in the same way its binary expansion is  $\underline{100111010}_2$ . Notice that because of the condition  $\overline{f_i^b}^X(\overline{c_0^b}^X) = \overline{undef}^X$  the expansion of a number cannot begin by a 0.

Operations can be added to the integers data structures, like the multiplication  $\times$ , depending of the basic operations considered for the algorithm.

**Definition 7 (Formula).** A formula F is a term with a particular form:

$F \stackrel{\text{def}}{=} true \mid false \mid R(t_1, \ldots, t_{\alpha}) \mid \neg F \mid (F_1 \wedge F_2) \text{ where } R \text{ is a relation symbol,}$ a function with output  $\overline{true}^X$  or  $\overline{false}^X$ ), and  $t_1, \ldots, t_{\alpha}$  are terms.

We say that a formula is true (resp. false) in X if  $\overline{F}^X = \overline{true}^X$  (resp.  $\overline{false}^X$ ).

**Definition 8 (Isomorphism).** Let X and Y be two structures with the same signature  $\mathcal{L}$ , and let  $\zeta : \mathcal{U}(X) \to \mathcal{U}(Y)$  be an application.  $\zeta$  is an isomorphism between X and Y if :

- 1.  $\zeta$  is surjective

- 2. For every symbol  $c \in \mathcal{L}$  with arity  $0, \zeta(\overline{c}^X) = \overline{c}^Y$ 3. For every  $f \in \mathcal{L}$  with arity  $\alpha > 0$ , and for every  $a_1, \ldots, a_\alpha \in \mathcal{U}(X)$ ,  $\zeta(\overline{f}^X(a_1, \ldots, a_\alpha)) = \overline{f}^Y(\zeta(a_1), \ldots, \zeta(a_\alpha))$

We say that two structures X and Y are isomorphic if there exists an isomorphism between them. Notice that if  $\zeta$  is an isomorphism between X and Y, then  $\zeta(\bar{t}^X) = \bar{t}^Y$ . And because we assumed that every signature contains the equality symbol then every isomorphism is injective. Therefore, we have that a = b in X if and only if  $\zeta(a) = \zeta(b)$  in Y. In particular, a formula F is true (resp. false) in X if and only if F is true (resp. false) in Y. Moreover, because  $\zeta$  is injective and by definition surjective, it is bijective. In particular we can introduce  $\zeta^{-1}$ , which is also an isomorphism.

## **B** The BSP bridging model of computation

## B.1 The notion of bridging model.

The traditional von Neumann (RAM) model has always served as the main model for designing sequential algorithm (Fig 2). It has also served as a reference model for hardware design. In the context of parallel algorithm design, no such ubiquitous model exists. The PRAM model (shared memory) allows a theoretical reasoning about parallel algorithms by highlighting the parallelism's degree of problems. Nevertheless, it makes a number of assumptions that cannot be fulfilled in HPC applications and hardware; mainly because the cost of communication is greater than that of computation and the number of processors is limited.

Fig. 2. The sequential model.

In computer science, a bridging model is thus an abstract model of a computer which provides a conceptual bridge between the physical implementation of the machine and the abstraction available to the programmer of that machine; in other words,

it is intended to provide a common level of understanding between hardware and software engineers. A bridging model provides software developers with an attractive escape route from the world of architecture-dependent parallel software. A successful bridging model is one which can be efficiently implemented in reality and efficiently targeted by programmers; in particular, it should be possible for a compiler to produce good code from a typical high-level language. The term was introduced in [23], which argued that the strength of the von Neumann model was largely responsible for the success of computing. The paper goes on to develop the BSP model as an analogous model for parallel computing. Even with rapidly changing technology and architectural ideas, hardware designers can still share the common goal of realizing efficient von Neumann machines, without having to be too concerned about the software that is going to be executed. Thus, the von Neumann model is the connecting bridge that enables programs from the diverse and chaotic world of software to run efficiently on machines from the diverse and chaotic world of hardware. An analogous bridging model for parallel computation is thus needed.

SoftwareAs the von Neumann modelParallel sortingprovides a unifying approach that<br/>can bridge the worlds of sequential<br/>hardware and software, so ValiantParallel FFT[23] sought for a unifying model<br/>that could provide an effective<br/>bridge between parallel hardware<br/>and software. The BSP model has

been introduced to better reflect the hardware design features of mainstream parallel computers, through the direct mode of BSP (assumed in this paper, Fig 3). The BSP model allows for efficient algorithm design without any overspecification requiring the use of a large number of parameters. The underlying parallel computer implementation is similarly not overspecified. Each processor can communicate directly with every other processor, providing complete control over how the data is distributed between the processors in every superstep.

To evaluate an architecture-independent model of parallel computation such as BSP is to consider it in terms of all of its properties which means (a) its usefulness as a basis for the design and analysis of algorithms; (b) its applicability across the whole range of general-purpose architectures and its ability to provide efficient, scalable performance on them; (c) its support for the design of fully-portable programs; and (d) software engineering tools such as those for correctness or debug can be easily adapted to programs of this bridging model.

Take for example, a proof of correctness of a GPU-like program. Although interesting in itself it cannot be used directly for clusters of PCs. A bridging model has the advantage that if a program is correct, then this is the case for "all" physical architectures. Note that it is also the case for portable libraries such as MPI but algorithm design would be clearly architecture independent, which will be not the case using a bridging model. Moreover, it is known and accepted that correctness of programs is more costly in terms of work than just programming and designing algorithms. Hence the choice in this work of the BSP bridging model to provide both portability for proofs and a model for algorithmic design and efficient programs.

There exist other bridging models of parallel computations but only BSP is widely used and accepted for algorithm design. The BSP model has also been used with success in a wide variety of problems. A complete book of numerical algorithms is [2] and many other algorithms can be found in the literature.

## B.2 The BSP model

The BSP architecture. We recall that a BSP computer is formed by 3 main components: (1) A set of  $\mathbf{p}$  homogeneous pairs of processors-memories (units); (2) A communication network to exchange messages between these units of computations; (3) A global synchronization unit to execute global synchronization barriers. A wide range of actual architectures can be seen as BSP computers. Clusters of PCs and multi-cores, GPUs, *etc.* can be thus considered as BSP computers. Share memory machines could also be used in a way such that each processor only accesses a sub-part of the shared memory (which is then "private") and communications could be performed using a dedicated part of the memory.

The BSP model ignores the particular topology of the underlying machine; this rules out any use of network locality in algorithm design. The model only considers two levels of locality, local (inside the processor) and remote (outside a processor), with remote access usually being more expensive than local ones.

**The execution model.** A BSP program is logically executed as a sequence of *super-steps*, each of which is divided into three successive disjointed *phases*: (1) Each unit only uses its local data to perform *sequential* computations and

to request *data transfers* to other units; (2) The network delivers the requested data; (3) A *barrier* occurs, making the transferred data available for the next super-step. This *structured* model enforces a strict *separation* of communication and computation: during a super-step, no communication between the processors is allowed apart from transfer requests; only at the synchronization *barrier* is information actually exchanged. Messages sent in the previous superstep are available at the destination only at the start of the next superstep.

For performance, a BSP library can also send messages during the computation phase, but this is hidden to programmers. The best know examples being the BSPLIB for the C language and HAMA [20] for JAVA. A MPI program using *collective operations* only can also be viewed as a BSP program.

The cost model. The BSP model gives us a cost model that is both tractable and accurate. The *performance* of a BSP computer is characterized by 4 *parameters*: (1) The local processing speed **r**; (2) The number of processors **p**; (3) The time **L** required for a barrier; (4) The time **g** for collectively delivering a 1-relation which is a collective exchange where every processor receives/sends at most one word. The network can deliver an *h*-relation in time  $\mathbf{g} \times h$ .

The execution time (cost) of a super-step s is the sum of the maximal local processing time, the data delivery and the global synchronization times. The total cost (execution time) of a BSP algorithm is the sum of its super-step costs.

The partitioning of the data is a crucial issue. In fact, the choice of a distribution is one of the main means of influencing the performance of the algorithm. This leads to an emphasis on problem dependent techniques of data partitioning, instead of on hardware dependent techniques that take network topologies into account. The algorithm designer who is liberated from such hardware considerations may concentrate on exploiting the essential features of the problem.

## B.3 Advantages and Disadvantages

This *structured* model of parallelism enforces a strict separation of communication and computation. This execution policy has three main advantages. Firstly, it removes non-determinism and guarantees the absence of deadlocks. This is also simply the most visible aspect of a parallel model that shifts the responsibility for timing and synchronisation issues from the applications to the communications library<sup>3</sup>. Secondly, it allows for an accurate model of performance prediction based on the throughput and latency of the network, and on the speed of processors. This performance prediction model can even be used at runtime to dynamically make decisions, for instance to choose whether to communicate in order to re-balance data, or to continue an unbalanced computation. Furthermore, barriers have also a number of attractions: it is harder to introduce the possibility of livelock, since barriers do not create circular data dependencies. Barriers also permit novel forms of fault tolerance. Third, because any BSP algorithm is

<sup>&</sup>lt;sup>3</sup> BSP libraries are generally implemented using MPI or low level routines of the given specifics architectures.

organized as a sequence of supersteps, this makes it straightforward to extend techniques for constructing sequential algorithms to/from BSP algorithms.

The BSP model considers communication actions *en masse*. This is less flexible than asynchronous messages, but easier to debug since there are many communication actions in a parallel program, and their interactions are typically complex. Bulk sending also provides better performances since, from an implementation point of view, grouping communication together in a separate program phase permits a global optimisation of the data exchange by the communications library. Moreover it is easy to measure during the execution of a BSP program, time speeding to communicate and to synchronise by just adding chronos before and after the primitive of synchronization. This facility is mainly uses to compare different programs.

However, on most distributed multicore architectures, barriers are often expensive when the number of processors dramatically increases. Using BSP, programmers and designers have to keep in mind that some patterns are not BSP friendly: For example, BSP does not effectively manage pipeline and master/slave paradigms (farm of processes). Even if the BSP cost analysis proposes a method of estimating the work of a parallel algorithm, such a technique is not widespread: it seems that too many programmers still prefer using asynchronous send/received primitives (with potential data-races, deadlocks, *etc.*) instead of a structured model. We follow [10] that this manner of programming, as is the case with the "goto" statement, will be phased out in time (we can already see this for big-data frameworks such as PREGEL [14], MAPREDUCE [20], *etc.*).

Moreover, the BSP model, as a coarse-grained model of computation, has been proved to be very appropriate for problems with regular data-structures, and so, for problems based on domain decomposition. For irregular structures, some heuristics can improve the balance efficiently. But that is not as natural as spawning small processes (or threads) of calculation of each irregular part of the structure. That is the main inconvenient of the model.

## B.4 Programming using BSP

BSP is thus defined as a distributed memory model with point-to-point communication between processors. The computation is divided into supersteps separated by global synchronization steps, and packets sent in one superstep are assumed to be delivered at the beginning of the next superstep. Each processor can communicate directly with every other processor, providing complete control over how the data is distributed between the processors in every superstep.

We now present the main libraries for BSP programming. The reader can thus understand why our communication function in ASM presented in Section D is sufficient to express most (all?) typical BSP algorithms. We do not present all the primitives but the most important ones only.

The standard BSPlib. The BSPLIB<sup>4</sup> [12] is a C library of communication routines. It aims to support the development of parallel algorithms based on the BSP model. It offers routines for both message passing (BSMP) and remote memory access (DRMA). The development of shared-memory based possibilities is justified by the intense use of DRMA routines in numerical algorithms. It is interesting to note that about 20 routines are available only, compared to the more than 200 that composed MPI. The BSPLIB is thus easier to understand and to use, without lack of expressivity for programming HPC architectures.

Within a BSP computation, we can query some information about the machine: int bsp\_nprocs() returns the number of processors  $\mathbf{p}$  and int bsp\_pid() returns the processor identifier which belongs to  $0, ..., \mathbf{p} - 1$ . The barrier is done using void bsp\_sync() which blocks the node until all other nodes have called bsp\_sync and all messages sent to it have been received.

Sending a packet (in a buffering mode) is done using void bsp\_send(int pid, const void tag, const void payload, int payload\_bytes). The routine is based on the idea of a two-part message. A fixed-length part carries tag information that will help the receiver to interpret the message (tag); a variable-length part contains the main data payload. The length of the tag (payload\_bytes) is required to be fixed during any particular superstep, but can vary between supersteps. The destination buffer of a processor may be viewed as a queue where incoming messages are enqueued in an arbitrary order. If the message is not accessed within the superstep it is removed from the buffer.

The programmer can know the number of received messages as well as the total size of received data (in bytes) using the routine void bsp\_qsize(int packets, int accum\_nbytes). This routine works on the queue of received messages. To receive a message, the user should use the procedures void bsp\_get\_tag(int status, void tag) and void bsp\_move(void payload,int reception\_bytes).bsp\_get\_tag returns the tag of the first message in the queue and the size of the corresponding payload (status is -1 if the queue is empty). bsp\_move copies the payload of the first message of the system queue, *i.e.* the buffer call payload, and removes it from the queue. Then, the system will advance to the next message.

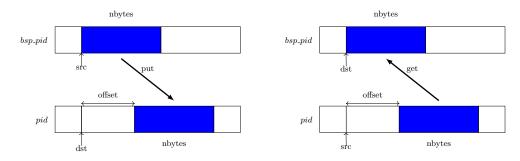

Registering or deleting a variable from global access is done using: void bsp\_push\_reg (const void ident, int size) and void bsp\_popregister(const void ident). Due to the SPMD structure of BSP programs, if *p* instances share the same name, they will not, in general, have the same physical address. To allow BSP programs to be executed correctly, the BSPLIB provides a mechanism for relating these various addresses by creating associations called registrations (not show here). Now, the two DRMA routines operations (Fig 4) are: (1) void bsp\_get(int pid,const void src,int offset, void dst,int nbytes) stands for global reading access; It copies *n* bytes to the local memory address —dst from the variable src at offset of the remote processor pid; (2) void bsp\_put(int pid,const void src,void dst,int offset, int nbytes) stands for global writing access; It copies *n* bytes from local memory src to dst at offset on remote processor pid. It is important to note that

<sup>&</sup>lt;sup>4</sup> http://www.bsp-worldwide.org/

Fig. 4. DRMA BSP operations: "put" and "get".

the get and put operations are executed during the synchronisation step and all get are served before a put overwrites a value.

The Paderborn University BSP is another library for C which is close to the BSPLIB. For BSP computing, the main differences come from sending routines. Sending a single message (buffer) can be done using void bsp\_send(int dest, void\* buffer, int size). After the calling, the buffer may be overwritten or freed. Each processor can access the received messages of type t\_bspmsg. This can be done using t\_bspmsg\* bsp\_findmsg(t\_bsp\* bsp, int id, int index) where id is the "id" of the source-node and index of the message. To access to the message, we need void\* bspmsg\_data(t\_bspmsg\* msg) which returns a pointer to the sending block of data and int bspmsg\_size(t\_bspmsg\* msg) which returns its size.

The BSPLIB has been recently implemented for multi-core<sup>5</sup> and GPUs  $^{6}$ . The PUB has been implementation for  $Java^7$  and in the context of big-data<sup>8</sup> [20].

**Other libraries** Another way is using the standard MPI notably the collective operations [2]. But it is the responsible of the programmer to follow the BSP model when using asynchronous sending (potential deadlock). The number of routines of MPI is huge and understanding all their interactions is for expert.

NESTSTEP<sup>9</sup> is a programming language,  $\dot{a}$  la C, dedicated to BSP. It adds a virtual shared memory where the memory consistency is relaxed (but deterministic) during supersteps. The main method of a program is executed by all available processors. The main primitives of NESTSTEP are the following: step: executes a statement in parallel; combine gather the results of the parallel execution (barrier); forall allows to parallel write (with barrier) to a shard array.

<sup>&</sup>lt;sup>5</sup> http://www.multicorebsp.com/

<sup>&</sup>lt;sup>6</sup> http://www.kunzhou.net/2008/BSGP.pdf

<sup>7</sup> http://www.lume.ufrgs.br/bitstream/handle/10183/18662/000731056.pdf; sequence=1

<sup>&</sup>lt;sup>8</sup> https://hama.apache.org/

<sup>&</sup>lt;sup>9</sup> http://www.ida.liu.se/~chrke55/neststep/index.html

PREGEL<sup>10</sup> [14] is a powerful (proprietary) language dedicated to graph algorithms. The approach centers around computations on the vertices of the graph. Each vertex of the graph has a unique "id", an associated value and a list of outgoing weighted edges. On each superstep, each worker node invokes a procedure Compute for each active vertex that is under its control. his procedure is responsible for the execution of the algorithm and is allowed, among other actions, to invoke other methods, compute new values for the vertex, add or remove vertices and edges, and send messages to other vertices. These messages are exchanged directly among the vertices, even if the vertices are being executed on different machines of the platform. The messages are sent asynchronously in order to allow the overlapping of computation and communication, but are delivered to the destination vertex only on the beginning of the next superstep. If a vertex declares that all its processing was done, it sends a message informing all the other nodes and deactivates itself. Any change on the topology is only performed on the next superstep, before the invocation of the Compute procedure.

Last is  $BSML^{11}$  [13], a functional (OCAML extension) language for BSP. It uses a small set of primitives which are working over parallel data structures called a *parallel vectors*. A vector expresses that each of the **p** processors *embeds* a value of any type. There is two primitives for the asynchronous manipulations of vectors and also two for the communications (barrier). These primitives and the use of vectors has been used (and adapted) to PYTHON<sup>12</sup> and C++<sup>13</sup>.

<sup>&</sup>lt;sup>10</sup> The free version: http://giraph.apache.org/

<sup>&</sup>lt;sup>11</sup> http://traclifo.univ-orleans.fr/BSML/

<sup>&</sup>lt;sup>12</sup> http://dirac.cnrs-orleans.fr/ScientificPython/

<sup>&</sup>lt;sup>13</sup> https://github.com/jfalcou/BSPPP

## C Proofs of technical lemmas

## C.1 Replacement in a Structure

**Definition 9 (Replacement in a Structure).** Let X be a structure, and let  $U_1 \subseteq \mathcal{U}(X)$  and  $U_2$  be two sets such that there exists a bijection  $\varphi$  from  $U_1$  to  $U_2$ . The structure Y obtained by replacing in X the elements of  $U_1$  by the elements of  $U_2$  is defined by:

1.

$$\mathcal{L}(Y) = \mathcal{L}(X)$$

2.

$$\mathcal{U}(Y) = (\mathcal{U}(X) \setminus U_1) \cup U_2$$

3. If  $c \in \mathcal{L}(X)$  is a 0-ary symbol then:

$$\overline{c}^Y \stackrel{\text{def}}{=} \begin{cases} \varphi(\overline{c}^X) \text{ if } \overline{c}^X \in U_1 \\ \overline{c}^X \text{ otherwise} \end{cases}$$

If  $f \in \mathcal{L}(X)$  is a  $\alpha$ -ary symbol with  $\alpha > 0$ , and  $a_1, \ldots, a_\alpha \in \mathcal{U}(Y)$ , then:

$$\overline{f}^{Y}(a_{1},\ldots,a_{\alpha}) \stackrel{\text{def}}{=} \begin{cases} \varphi\left(\overline{f}^{X}(a'_{1},\ldots,a'_{\alpha})\right) \text{ if } \overline{f}^{X}(a'_{1},\ldots,a'_{\alpha}) \in U_{1} \\ \overline{f}^{X}(a'_{1},\ldots,a'_{\alpha}) & \text{ otherwise} \end{cases}$$

$$where \ a' \stackrel{\text{def}}{=} \begin{cases} \varphi^{-1}(a) \text{ if } a \in U_{2} \\ a & \text{ otherwise} \end{cases}$$

A replacement in a structure is a structure. Moreover, we proved in [15] that the replacement is an isomorphism:

#### Lemma 5 (A Replacement is an Isomorphism).

If X is a structure,  $U_1 \subseteq \mathcal{U}(X)$  and  $U_2 \cap \mathcal{U}(X) = \emptyset$ , then the structure Y obtained by replacing in X the elements of  $U_1$  by the elements of  $U_2$  is isomorphic to X. Moreover, if T is a set of  $\mathcal{L}(X)$  terms closed by subterms and such that for every  $t \in T$ ,  $\overline{t}^X \notin U_1$ , then for every  $t \in T$ ,  $\overline{t}^X = \overline{t}^Y$ .

## **Proof.** See [15]

Therefore, according to the second postulate, a replacement with fresh values in one local memory of a state produced a state. We prove here the Lemma p.6 stating that every value in an update is a critical element:

## Lemma 6 (Critical Elements).

For every state  $(X^1, \ldots, X^p)$  of the parallel algorithm A, for every  $1 \le i \le p$ , if  $(f, a_1, \ldots, a_\alpha, b) \in \Delta^i(A, \overrightarrow{X})$  then  $a_1, \ldots, a_\alpha, b$  are interpretations in  $X^i$  of terms in T(A).

**Proof.** The proof is made by contradiction.

We assume that there exists an update  $(f, a_1, \ldots, a_\alpha, a_0) \in \Delta^i(A, \vec{X})$  such that at least one  $a_i$  is not an interpretation in  $X^i$  of a term in T(A).

Let v be a fresh value, and  $Y^i$  be the structure obtained by replacing  $a_i$  by v in  $X^i$ . According to the lemma 5,  $X^i$  and  $Y^i$  are isomorphic.

So, according to the second postulate, because  $\overrightarrow{X} = (X^1, \dots, X^i, \dots, X^p)$  is a state of  $A, \overrightarrow{Y} = (X^1, \dots, Y^i, \dots, X^p)$  is also a state of A.

Because  $a_i$  is not an interpretation in  $X^i$  of a term in T(A), the states  $(X^1, \ldots, X^i, \ldots, X^p)$  and  $(X^1, \ldots, Y^i, \ldots, X^p)$  coincide over T(A).

So, according to the third postulate,  $\Delta^i(A, \vec{X}) = \Delta^i(A, \vec{Y})$ .

But  $a_i \notin \mathcal{U}(Y^i)$ , so  $(f, a_1, \ldots, a_\alpha, a_0)$  cannot appear in  $\Delta^i(A, \vec{Y})$ , which contradicts  $(f, a_1, \ldots, a_\alpha, a_0) \in \Delta^i(A, \vec{X})$ .

We prove here the Lemma p.7 stating that for each step of the algorithm only a bounded amount of work is done:

## Lemma 7 (Bounded Set of Updates).

For every state  $(X^1, \ldots, X^p)$  of the parallel algorithm A, for every  $1 \le i \le p$ , # $\Delta^i(A, \vec{X})$  is bounded.

**Proof.** According to the Lemma 6, if  $(f, a_1, \ldots, a_\alpha, b) \in \Delta^i(A, \overrightarrow{X})$  then  $a_1, \ldots, a_\alpha, b$  are interpretations in  $X^i$  of terms in T(A).

But, according to the third postulate, T(A) is finite. So there exists a bounded number of possible  $a_1, \ldots, a_{\alpha}, b$  in  $\Delta^i(A, \vec{X})$ .